Mezipaměť procesoru

Mezipaměť procesoru

| Typ | Mezipaměť , paměť paměti , energeticky nezávislá paměť |

|---|

| Předcházet | Registr procesoru |

|---|

| Následován | Paměť počítače ( v ) |

|---|

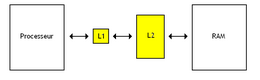

Procesor Cache je hardware mezipaměť používaný dané počítače centrální procesorové jednotky (CPU) ke snížení průměrné náklady (čas nebo energie) přístupu dat v hlavní paměti . Mezipaměť procesoru je menší a rychlejší paměť umístěná nejblíže k centrální procesorové jednotce (nebo jádru mikroprocesoru ), která ukládá kopie dat z umístění v hlavní paměti, která se často používají před jejich přenosem do registrů procesoru . Většina CPU má různé nezávislé mezipaměti, včetně instrukčních a datových mezipamětí, kde je mezipaměť dat obvykle organizována jako hierarchie více úrovní mezipaměti (L1, L2, L3, L4 atd.). Mezipaměti procesorů jsou součástí hlavní paměti, stejně jako registry procesorů a hlavní paměť, jsou nezbytné pro fungování počítače.

Všechny moderní (rychlé) procesory, až na několik výjimek, mají více úrovní mezipaměti procesorů. První procesory, které používaly mezipaměť, měly pouze jednu úroveň mezipaměti; na rozdíl od pozdějších mezipamětí nejvyšší úrovně nebyl rozdělen na L1d (pro data) a L1i (pro příkazy). Téměř všechny současné CPU s mezipamětí mají rozdělenou mezipaměť L1. Mají také mezipaměti L2 a pro větší procesory také mezipaměti L3. Mezipaměť L2 obvykle není rozdělena a funguje jako společné úložiště pro již rozdělenou mezipaměť L1. Každé jádro ve vícejádrovém mikroprocesoru má vyhrazenou mezipaměť L1 a obvykle se mezi jádry nesdílí. Mezipaměť L2 a mezipaměti nejvyšší úrovně lze sdílet mezi jádry. L4 cache v současnosti vzácná a je typicky nalézt na jakési dynamické paměti s náhodným přístupem (DRAM), spíše než statická random access memory s náhodným přístupem (SRAM), na integrovaném obvodu hubice nebo samostatného mikročipem (Výjimečně eDRAM typ mezipaměti plechovky použít pro všechny úrovně mezipaměti, až do L1). Historicky tomu tak bylo i v případě mezipaměti L1, kde větší čipy umožňovaly její integraci a obecně na všech úrovních mezipaměti, snad s výjimkou poslední úrovně. Každá další úroveň mezipaměti je optimalizována odlišně a má tendenci být větší než ta předchozí.

Existují i jiné typy mezipaměti, jako je překladová vyrovnávací paměť (TLB), která je součástí jednotky správy paměti (MMU) a která je přizpůsobena většině procesorů.

Poznámky a odkazy

- (fr) Tento článek je částečně nebo zcela převzat z anglického článku Wikipedie s názvem „ CPU cache “ ( viz seznam autorů ) .

- Franck Delattre, „ L'architecture Intel Nehalem “ , na hardware.fr , BeHardware ,17. září 2008(zpřístupněno 29. ledna 2020 )